### **Ptolemy Hardware/Software Interface Document**

Issue: 5

**Document Number:** RO-LPT-OU-TN-3401

Date: 3rd April 2001

# **MODULUS Ptolemy**

# Hardware Software Interface Document

Document: RO-LPT-OU-TN-3401

3rd April 2001

Prepared by:

D.L.Drummond

Modulus Team

Approved by:

.....

Authorised by:

.....

## Ptolemy Hardware/Software Interface Document

Issue: 5

Document Number: RO-LPT-OU-TN-3401

Date: 3rd April 2001

### CHANGE RECORD

| DATE                                  | CHANGE DETAILS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ISSUE |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 3rd March 2000                        | Draft issue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | draft |

| 22nd March 2000                       | Draft 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | draft |

| 27th March 2000                       | Draft 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | draft |

| 4th May 2000                          | Draft 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | draft |

| 8th May 2000                          | Draft 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | draft |

| 9th May 2000                          | First Issue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1     |

| 14th June 2000                        | 2.10 – analogue HK; new channels inserted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2     |

| 26th July 2000<br>11th September 2000 | <ul> <li>2.2 - corrections to map of I/O pages (in binary column) <ul> <li>DAC chan/data register to be written with 3 wait states</li> </ul> </li> <li>2.6 - added motor target positions to analogue o/p chans</li> <li>2.9 - added motor drive enables to critical functions</li> <li>2.10 - changes to analogue channel assignments <ul> <li>ADC now gives 16 bit 2's complement o/p</li> </ul> </li> <li>2.2 - RF freq. DAC added</li> <li>2.9 - Corrections and clarification for docking station motor drive bits</li> <li>2.10 - some analogue channel assignments changed. <ul> <li>pressure sensor sensitivites changed to reflect 2.5V</li> </ul> </li> </ul> | 3     |

| 19th March 2001                       | operation. Units column removed<br>Changes to pressure sensors<br>Revised calibration for docking station position monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.0   |

| 3rd April 2001                        | 2.10 - Revised conversions and shift counts for some HK analogue parameters. esp. pressure sensors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5.0   |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

## Ptolemy Hardware/Software Interface Document

Issue: 5

Document Number: RO-LPT-OU-TN-3401

Date: 3rd April 2001

### **CONTENTS**

| 1. IN' | TRODUCTION                                                       | 4  |

|--------|------------------------------------------------------------------|----|

| 1.1    | DEFINITIONS, ACRONYMS AND ABBREVIATIONS                          | 4  |

| 1.1    |                                                                  |    |

| 1.1    |                                                                  |    |

| 1.2    | References                                                       |    |

| 1.2    |                                                                  |    |

| 1.2    |                                                                  |    |

| 2. PR  | ROCESSOR MEMORY MAP                                              | 6  |

| 2.1    | OVERVIEW                                                         | 6  |

| 2.1    | MAP OF I/O PAGES                                                 |    |

| 2.2    | PROCESSOR CARD STATUS & PAGE REGISTERS                           |    |

| 2.3    | SCIF (LANDER INTERFACE)                                          |    |

| 2.4    |                                                                  |    |

| 2.4    | 1 0                                                              |    |

| 2.5    | °                                                                |    |

| 2.5    |                                                                  |    |

| 2.5    |                                                                  |    |

| 2.5    |                                                                  |    |

| 2.5    | • • • •                                                          |    |

| 2.5    |                                                                  |    |

| 2.5    |                                                                  |    |

| 2.5    |                                                                  |    |

| 2.5    |                                                                  |    |

| 2.5    |                                                                  |    |

|        | 5.10 I2C_Port_2 – non-destructive read of I2C received data      |    |

|        | 5.11 Soft_Ctrl_Port                                              |    |

|        | 5.12 DACC_Port – DAC counter port                                |    |

|        | 5.13 RFClk_Port_1 – RF clock generator I/F port 1                |    |

|        | 5.14 RFClk_Port_2 – RF clock generator I/F port 2 – tickle clock |    |

|        | 5.15 Assignment of WGA outputs                                   |    |

| 2.6    |                                                                  |    |

| 2.6    |                                                                  |    |

| 2.6    |                                                                  |    |

| 2.6    |                                                                  |    |

| 2.7    |                                                                  |    |

| 2.7    |                                                                  |    |

| 2.7    |                                                                  |    |

| 2.7    | 1 0                                                              |    |

| 2.8    | DIGHITAL (ON/OFF) CHANNELS                                       |    |

| 2.8    |                                                                  |    |

| 2.8    |                                                                  |    |

| 2.8    |                                                                  |    |

| 2.9    | CRITICAL FUNCTION CHANNELS                                       |    |

| 2.9    | 0.1 Critical functions register                                  | 19 |

| 2.9    |                                                                  |    |

| 2.10   | ANALOGUE HK CHANNELS                                             |    |

| 2.1    | 10.1 Thermocouples and pressure sensors                          | 23 |

| 2.1    | 10.2 Reference junction temperature                              |    |

### **Ptolemy Hardware/Software Interface Document**

Issue: 5

**Document Number:** RO-LPT-OU-TN-3401

Date: 3rd April 2001

#### INTRODUCTION

This document describes the hardware/software interface for the electronics box controlling the Ptolemy experiment on the Rosetta Lander. All hardware registers are memory mapped

#### 1.1 Definitions, acronyms and abbreviations

#### 1.1.1 Definitions

#### **Bit numbering:**

Bits are numbered with the least significant bit as bit 0 and most significant bit as bit 15. This is the numbering used in the HS-RTX-2010RH processor reference manual, in the schematics for the electronics and in other hardware documents:

| ms |    |    |    |    |    |   |   |   |   |   |   |   |   |   | ls |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|----|

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

It should be noted that the software documentation (URD, SDD), numbers bits in the reverse order (most significant bit is bit 0, least significant bit is bit 15) as is usual with space data systems.

#### **Instrument/Experiment:**

As Roland is, itself, considered to be an instrument of the Rosetta spacecraft, this document refers to Ptolemy as an "experiment" or "subsystem"

#### 1.1.2 Acronyms

| ADC   | Analogue to Digital Converter                                                   |

|-------|---------------------------------------------------------------------------------|

| ASIC  | Applications Specific Integrated Circuit (i.e a custom chip)                    |

| CDMS  | Command and Data Management System (Lander on-board computer)                   |

| DAC   | Digital to Analogue Converter                                                   |

| FPGA  | Field Programmabel Gate Array (such as the ACTEL chip on processor card)        |

| HK    | House Keeping - telemetry required to confirm correct operation of instrument   |

| HT    | High Tension (high voltage - ~2kV in this case)                                 |

| HV    | High voltage (same as HT)                                                       |

| I2C   | Inter-IC - a serial bus protocol for transfering data between ICs.              |

| IC    | Integrated Circuit                                                              |

| MIPS  | Millon Instructions Per Second                                                  |

| MORSP | Modulus On-board Real-time Software (Ptolemy)                                   |

| OU    | Open University                                                                 |

| PWM   | Pulse Width Modulation                                                          |

| RAL   | Rutherford Appleton Laboratory                                                  |

| RICA  | Rosetta Ion-Counter ASIC – one of the ASICs used to control & read the Ion-trap |

| SCIF  | Space Craft Interface – FPGA that controls interface with the Lander CDMS       |

| TC    | Telecommands                                                                    |

| Tlm   | Telemetry                                                                       |

| ТМ    | Telemetry                                                                       |

| VCO   | Voltage Controlled Oscillator                                                   |

| WGA   | Waveform Generator ASIC – the other ASIC used to control & read the Ion-trap    |

### Ptolemy Hardware/Software Interface Document

Issue: 5

Document Number: RO-LPT-OU-TN-3401

Date: 3rd April 2001

#### 1.2 References

#### 1.2.1 Applicable Documents

| AD1 |                  | REID-A                                              |

|-----|------------------|-----------------------------------------------------|

| AD2 | ESA PSS 05       | Software Engineering Standards                      |

| AD3 | BSC(96)2 issue 1 | Guide to applying PSS 05 to small software projects |

### 1.2.2 Reference Documents

| RD1 | RO-PTO-RS-0001/EID B | REID-B                                                |

|-----|----------------------|-------------------------------------------------------|

| RD2 |                      | Ptolemy Operations Plan                               |

| RD3 | RO-BER-RAL-TN-3401   | WGA and RICA applicability to RF Scan Function Design |

### **Ptolemy Hardware/Software Interface Document**

Issue: 5

**Document Number:** RO-LPT-OU-TN-3401

Date: 3rd April 2001

#### 2. PROCESSOR MEMORY MAP

#### 2.1 Overview

The overall memory map for the electronics box is shown below. The total address space is 1048576 bytes (a 20 bit address bus) This comprises 16 pages each of 65536 bytes. The first 2 pages of memory are occupied by fuse-link PROM (containing the baseline flight software) and the top 8 pages are static RAM for variables and copied program code. Above the fuse-link PROM are two pages allocated to I/O registers and, above these, 4 pages (4,5,6 & 7) occupied by EEPROM and are intended for storing patches and updated tables.

| FFFFF |                           |   |            |                                                   |

|-------|---------------------------|---|------------|---------------------------------------------------|

|       | 256 k bytes RAM           |   |            |                                                   |

|       |                           |   | I/O addres | ss space:                                         |

| C0000 |                           |   |            |                                                   |

| BFFFF |                           | Л |            |                                                   |

|       | 256 k bytes RAM           |   | 3С000Н:    | peripherals<br>with 3 wait<br>states              |

| 80000 |                           |   | 38000H:    | peripherals<br>with no wait<br>states             |

| 7FFFF |                           |   |            | Blatch                                            |

|       | 256 k bytes EEPROM        |   | 34000H:    | RICA (ASIC) for<br>Ion trap ctrl &<br>acquisition |

| 40000 |                           | / | 2000077    | Not used on                                       |

| 3FFFF |                           | / | 30000H:    | Not used on<br>Ptolemy                            |

| 51111 | 128 k bytes I/O addresses |   |            | -                                                 |

| 20000 | 5                         |   |            |                                                   |

|       |                           |   | 2C000H:    | S/C interface                                     |

| 1FFFF | 128 k bytes PROM          |   |            | Actel                                             |

| 00000 |                           |   |            |                                                   |

|       |                           |   | 28000H:    | processor card<br>Actel register<br>2 (code page) |

|       |                           |   | 24000H:    | processor card<br>Actel register<br>1 (status)    |

|       |                           |   | 20000H:    | processor card<br>Actel register<br>0 (status)    |

### **Ptolemy Hardware/Software Interface Document**

Issue: 5

Document Number: RO-LPT-OU-TN-3401

Date: 3rd April 2001

#### 2.2 Map of I/O pages

The table below shows an overall map of the I/O pages. All I/O registers are at even addresses and should be accessed with a word read or write instruction, even if they have no meaningful bits in the upper byte.

| Addr range  | Description                                 | Address format (binary)  |

|-------------|---------------------------------------------|--------------------------|

| 20000-23FFE | Low byte of processor card status register  | 0010 00xx xxxx xxxx xxx0 |

| 24000-27FFE | High byte of processor card status register | 0010 01xx xxxx xxxx xxx0 |

| 28000-2BFFE | Processor board page register               | 0010 10xx xxxx xxxx xxx0 |

| 2C000-2FFFE | SCIF – Lander interface FPGA                | 0010 11xx xxxx xxxx xss0 |

| 30000-33FFE | Not used for Ptolemy                        | 0011 00xx xxxx xxxx xxx0 |

| 34000-37FFE | RICA (Ion trap control)                     | 0011 01xx xxxx xxrr rrr0 |

|             |                                             |                          |

| 38000-3BFFE | Other peripherals with no wait states:      | 0011 10                  |

|             |                                             |                          |

| 38000-3800E | Telemetry channel select (W)                | 0011 10xx xxxx 0000 xxx0 |

| 38010-3801E | Trigger ADC (W)                             | 0011 10xx xxxx 0001 xxx0 |

| 38020-3802E | ADC result register (R)                     | 0011 10xx xxxx 0010 xxx0 |

| 38080-3808E | Not used                                    | 0011 10xx xxxx 1000 xxx0 |

| 38090-3809E | DAC enable register                         | 0011 10xx xxxx 1001 xxx0 |

| 380A0-380AE | Valve data (on/off) register                | 0011 10xx xxxx 1010 xxx0 |

| 380B0-380BE | Valve data (on/off) enable register         | 0011 10xx xxxx 1011 xxx0 |

| 380C0-380CE | PWM data register                           | 0011 10xx xxxx 1100 xxx0 |

| 380D0-380DE | PWM enable register                         | 0011 10xx xxxx 1101 xxx0 |

| 380E0-380EE | Critical functions register                 | 0011 10xx xxxx 1110 xxx0 |

| 380F0-380FE | Critical functions enable register          | 0011 10xx xxxx 1111 xxx0 |

|             |                                             |                          |

| 3C000-3FFFE | Peripherals with 3 wait states              | 0011 11                  |

|             |                                             |                          |

| 3C070-3C07E | Set RF Frequency DAC                        | 0011 10xx xxxx 0111 xxx0 |

| 3C080-3C08E | DAC chan/data register                      | 0011 11xx xxxx 1000 xxx0 |

xx... - don't care; the read shall access the same register whatever the contents of this field

ss - this bit field selects an internal register in the SCIF FPGA

rrrrr - this bit field selects an internal register in the RICA ASIC

The 3-wait state option is only forseen for writes to the DAC chan/status register and the RF frequency DAC. For these registers 3 wait states are mandatory and the address 3C0XX should always be used instead of 380XX

### **Ptolemy Hardware/Software Interface Document**

Issue: 5

Document Number: RO-LPT-OU-TN-3401

Date: 3rd April 2001

#### 2.3 Processor card status & page registers

The processor card status is contained in a 16 bit register in the processor card FPGA. Because, to save pins, only the low 8 bits of the data bus are connected to the processor card FPGA, this register is implemented as two 8 bit registers (plus a 4 bit register for saving the code page) at addresses 20000H (0010 00xx xxxx xxxx xxx0) for the low byte and 24000H (0010 01xx xxxx xxxx 0) for the high byte (and 28000H or 0010 10xx xxxx xxxx xxx0 for the code page register).

| MS bit   |                    | Processor status low byte (20000H) |                     |                     |                      |                           |                            |  |  |  |  |  |  |

|----------|--------------------|------------------------------------|---------------------|---------------------|----------------------|---------------------------|----------------------------|--|--|--|--|--|--|

| 7        | 6                  | 5                                  | 4                   | 3                   | 2                    | 1                         | 0                          |  |  |  |  |  |  |

| INH1 (R) | SW NMI<br>#2 (R/W) | SW NMI<br>#1 (R/W)                 | EEPROM<br>ready (R) | Current<br>trip (R) | Wdog<br>NMI<br>(R/W) | SW sys.<br>Reset<br>(R/W) | SW proc.<br>Reset<br>(R/W) |  |  |  |  |  |  |

| MS bit        |               | Processor status high byte (24000H) Ls bit                                 |                            |                               |                           |               |          |  |  |  |  |  |  |

|---------------|---------------|----------------------------------------------------------------------------|----------------------------|-------------------------------|---------------------------|---------------|----------|--|--|--|--|--|--|

| 7(15)         | 6(14)         | 6(14)         5(13)         4(12)         3(11)         2(10)         1(9) |                            |                               |                           |               |          |  |  |  |  |  |  |

| Spare<br>(R0) | Spare<br>(R0) | EEPROM<br>Int clear<br>R(1)/W                                              | EEPROM<br>protect<br>(R/W) | I-trip int<br>clear<br>R(1)/W | Wdog<br>restart<br>R(0)/W | Spare<br>R(0) | INH2 (R) |  |  |  |  |  |  |

R - read only

R(0) - always reads 0

R(1) - always reads 1

R/W - read/write

SW - software

## Ptolemy Hardware/Software Interface Document

Issue: 5

Document Number: RO-LPT-OU-TN-3401

Date: 3rd April 2001

| Bit/ | Bit/ |                               | Function                                                                                                                                                                                                                       |

|------|------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| word | byte |                               |                                                                                                                                                                                                                                |

| 1.5  | -    |                               | High byte                                                                                                                                                                                                                      |

| 15   | 7    | Spare (R0)                    | This bit is not currently used and always reads as 0                                                                                                                                                                           |

| 14   | 6    | Spare (R0)                    | This bit is not currently used and always reads as 0                                                                                                                                                                           |

| 13   | 5    | EEPROM<br>Int clear<br>R(1)/W | The software should write a 0 to this bit to clear the "EEPROM ready" interrupt (EI4). The bit always reads 1                                                                                                                  |

| 12   | 4    | EEPROM<br>protect<br>(R/W)    | <ul> <li>= 0: EEPROM disabled; reading and writing to EEPROM is prevented</li> <li>= 1: EEPROM enabled; reading allowed. Writing allowed provided correct pattern is sent to enable it.</li> </ul>                             |

| 11   | 3    | I-trip reset<br>R(1)/W        | The software should write a 0 to this bit to clear the current trip maskable interrupt, EI5 (and the current trip flag in bit 3). This bit always reads 1                                                                      |

| 10   | 2    | Wdog<br>restart<br>R(0)/W     | The software should write a 1 to this bit to restart the watchdog timer. If it fails to do this within 1s of the previous restart (or power-on) the watchdog NMI is invoked. After a further 1s the watchdog reset is invoked. |

| 9    | 1    | Spare<br>R(0)                 | This bit is not currently used and always reads as 0                                                                                                                                                                           |

| 8    | 0    | INH2 (R)                      | This bit reflects the state of the Chemistry set inhibit 2 signal.                                                                                                                                                             |

|      |      |                               | Low byte                                                                                                                                                                                                                       |

| 7    | 7    | INH1 (R)                      | This bit reflects the state of the Chemistry set inhibit 1 signal                                                                                                                                                              |

| 6    | 6    | SW NMI<br>#2 (R/W)            | This bit may be set by the software to generate an NMI. The NMI condition shall be cleared by hardware on interrupt acknowledge but the bit shall remain set until reset or until cleared by software.                         |

| 5    | 5    | SW NMI<br>#1 (R/W)            | This bit has the same function as bit 6                                                                                                                                                                                        |

| 4    | 4    | EEPROM<br>ready (R)           | This bit reads 1 when the EEPROM is ready for writing (has completed a previous write). It goes to 0 when an EEPROM write is initiated.                                                                                        |

| 3    | 3    | Current<br>trip (R)           | This bit is set when a current trip interrupt is requested. This also initiates external interrupt 5 which may be cleared by writing 0 to bit 11.                                                                              |

| 2    | 2    | Wdog<br>NMI<br>(R/W)          | This bit is set to 1 by the hardware to indicate that a watchdog NMI has occurred. The software may clear this bit by writing a 0 to it.                                                                                       |

| 1    | 1    | SW sys.<br>Reset<br>(R/W)     | The processor writes a 1 to this bit to assert the system reset. This pulls<br>low a reset line to all boards on the backplan except the processor card.<br>The software releases the reset by writing a 0 to this bit.        |

| 0    | 0    | SW proc.<br>Reset<br>(R/W)    | The software may reset the processor card by writing a 1 to this bit. The processor shall then be restarted. This bit shall remain at 1 and must be cleared before a further reset can be generated in this way.               |

The functions of the bits defined above are described in the following table:

### **Ptolemy Hardware/Software Interface Document**

Issue: 5

**Document Number:** RO-LPT-OU-TN-3401

Date: 3rd April 2001

The Processor card page register is a 4 bit read/write register that is intended to be used by the flight software to store the current program memory page number. Writing a value to this register does not, however, directly affect the addressing of memory; it is purely a storage location.

The register has the following format:

| MS | Processor Card Page Register (28000H) |                                   |  |  |  |  |  |  |  |  |  |  |   | LS |

|----|---------------------------------------|-----------------------------------|--|--|--|--|--|--|--|--|--|--|---|----|

| 15 | 14                                    | 14 13 12 11 10 9 8 7 6 5 4 3 2 1  |  |  |  |  |  |  |  |  |  |  | 0 |    |

| U  | U                                     | U U U U U U U 0 0 0 0 page (0-15) |  |  |  |  |  |  |  |  |  |  |   |    |

U – undefined; these bits shall probably contain the last value to be placed on the data bus. As the processor card FPGA is not connected to the high 8 bits of the data bus, it cannot force these bits to zero.

#### 2.4 SCIF (Lander interface)

The SCIF is an FPGA on the Ptolemy backplane that handles the TC/TM interface between the ptolemy processor card and the Lander CDMS. It has the following registers:

| Addr  | Address format (x -> don't care) | R/W   | Description                       |

|-------|----------------------------------|-------|-----------------------------------|

| 2C000 | 0010 11xx xxxx xxxx x000         | Read  | Interrupt Register                |

| 2C002 | 0010 11xx xxxx xxxx x010         | Read  | Status register (TC/TM status)    |

| 2C004 | 0010 11xx xxxx xxxx x100         | Read  | Received data register (TC data)  |

| 2C006 | 0010 11xx xxxx xxxx x110         | Read  | Not used                          |

|       |                                  |       |                                   |

| 2C000 | 0010 11xx xxxx xxxx x000         | Write | Not used                          |

| 2C002 | 0010 11xx xxxx xxxx x010         | Write | Status register (TC/TM status)    |

| 2C004 | 0010 11xx xxxx xxxx x100         | Write | Not used                          |

| 2C006 | 0010 11xx xxxx xxxx x110         | Write | Transmit data register (TM words) |

#### 2.4.1 Interrupt register

The low 3 bits of the interrupt register show the status of the three interrupt sources. The upper 13 bits always read 0:

| MS |    |                                  |  |  | Ir | nterrup | t Regis | ster (32 | C000H | I) |  |  |  |  | LS |

|----|----|----------------------------------|--|--|----|---------|---------|----------|-------|----|--|--|--|--|----|

| 15 | 14 | 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |  |  |    |         |         |          |       |    |  |  |  |  |    |

| 0  | 0  | 0 0 0 0 0 0 0 0 0 0 0 0 0 C B    |  |  |    |         |         |          |       |    |  |  |  |  | Α  |

The interrupt sources are as follows:

| Source | Mode     | Description                                                                                                                                                                                         |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| А      | Any      | When set, indicates the arrival of an Address word synchron. The received data register (at address 2C004H) contains the address word that caused the interrupt request.                            |

| В      | Receive  | When set, indicates the arrival of a CMD/data synchron while the interface was selected and was in receive mode. The received data register (at address 2C004H) contains the received command word. |

| С      | Receive  | When set, indicates the arrival of a Status synchron. The status register (address 2C002H) has been copied and is being transmitted.                                                                |

| С      | Transmit | When set, indicates the arrival of a data synchron. The telemetry data register (address 2C006H) has been copied and is being transmitted. The next TM data word may now be written.                |

### **Ptolemy Hardware/Software Interface Document**

Issue: 5

Document Number: RO-LPT-OU-TN-3401

Date: 3rd April 2001

When one or more of the above events occur, an external interrupt 2 (EI2) is generated. Reading the interrupt register clears the interrupt request and sets A, B and C back to 0. The EI4 handler, after reading the interrupt register to acertain the source(s) of the interrupt, should check each of bits A, B and C and take the appropriate action in case of any one of them being set.

#### 2.4.2 Status register

This is a read/write register holding the interface communications status. Most of the bits are hard wired to 0 or 1 and always read the same:

| MS | Status Register (2C002H) |                                  |   |   |    |    |    |   |   |   |   |     |    |   | LS |

|----|--------------------------|----------------------------------|---|---|----|----|----|---|---|---|---|-----|----|---|----|

| 15 | 14                       | 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |   |   |    |    |    |   |   |   |   |     |    | 0 |    |

| 0  | 0                        | 1                                | 1 | 0 | ME | CE | SR | 1 | 0 | 0 | 0 | BSY | SM | 0 | 0  |

| 10 | ME  | Message Error flag. The software should set this flag to 1 if it receives a subsystem    |

|----|-----|------------------------------------------------------------------------------------------|

|    |     | address word with an illegal function code                                               |

| 9  | CE  | Count Error flag. The software should set this flag to 1 if it receives a message whose  |

|    |     | length does not agree with the value given in the SSADR word                             |

| 8  | SR  | The software sets this bit to indicate that it has a service request to the CDMS. It     |

|    |     | should clear the flag once the CDMS has responded with a "send request" message.         |

| 3  | BSY | Busy flag. The software sets this to indicate that it is unable to comply with a CDMS    |

|    |     | request. Use to be avoided if possible – not planned for Ptolemy.                        |

| 2  | SM  | The software may set this flag to indicate that it is in sleep mode. Use not planned for |

|    |     | Ptolemy                                                                                  |

The following bits are significant:

The status word is automatically transmitted by the hardware on receipt of a "send status" synchron from the CDMS. Such a synchron is sent at the end of each command message and at the end of each HK request. In order for the status word transmitted to reflect the up-to-date status of the interface, the status must be updated within  $38\mu s$  of receiving an address word or a command word.

### **Ptolemy Hardware/Software Interface Document**

Issue: 5

Document Number: RO-LPT-OU-TN-3401

Date: 3rd April 2001

#### 2.5 RICA

The RICA appears at address 34000H (more exactly, in all the 64 byte windows from 34000H to 37FC0H). The RICA contains 32 word addresses, 24 of which are used. The registers have even addresses (address bit 0 should always be 0).

| Addr   | Name          | R/W   | Description                                                      |

|--------|---------------|-------|------------------------------------------------------------------|

| 34000  | FIFO_Port_1   | Read  | Read low word (bits 15:0) from FIFO, word removed from FIFO      |

| 34002  | FIFO_Port_2   | Read  | Interrogative read bits 25:16 of FIFO data + valid & error flags |

| 34004  | FIFO_Port_3   | Read  | Reads FIFO how full (10 bit count) + empty and full flags        |

| 34006  | FIFO_Port_4   | R/W   | Read or write pattern to/from FIFO flip register bits 15:0       |

| 34008  | FIFO_Port_5   | R/W   | Read or write pattern to FIFO flip register bits 30:16           |

| 3400A  | FIFO_Port_6   | Read  | Reads FIFO vector bits 4:0                                       |

| 3400C  | FIFO_Port_7   | Write | Write test data (bits 5:0), test count (bits 9:0)                |

| 3400C  | FIFO_Port_7   | Read  | Read test count (9:0) + flags: test complete, success, failure   |

| 3400E  | FIFO_Port_8   | Read  | Read code bits (15:0) for test_mux=0, bits(30:16) for test_mux=1 |

| 34010  | I2C_Port_1    | Write | Write data to I2C transmit register (16 bit word)                |

| 34010  | I2C_Port_1    | Read  | Permanent read from I2C receive register (16 bit word)           |

| 34012  | I2C_Port_2    | Read  | Interrogative read from I2C receive register                     |

| 34014  | Soft_Ctl_Port | R/W   | Set/clear/read software resets and test controls                 |

| 34016  | DACC_Port     | R/W   | RICA DAC o/p bits (11:0) write or read back                      |

| 34018  | RFClk_Port_1  | R/W   | 8 bit divider for RF clock (not used for Ptolemy)                |

| 3401A  | RFClk_Port_2  | R/W   | 8 bit divider for tickle clock (not used for Ptolemy)            |

| 3401C  | Wdog_Port     | R/W   | Read/Write the RICA watchdog (no use planned for Ptolemy)        |

| 3401E  | Not used      |       |                                                                  |

| 34020  | Exp_Port_B_0  | Write | Expansion port 0 – write 16 bits to exp bus with decode 0 active |

| 34022  | Exp_Port_B_1  | Write | Expansion port 1 – write 16 bits to exp bus with decode 1 active |

| 34024  | Exp_Port_B_2  | Write | Expansion port 2 – write 16 bits to exp bus with decode 2 active |

| 34026  | Exp_Port_B_3  | Write | Expansion port 3 – write 16 bits to exp bus with decode 3 active |

| 34028  | Exp_Port_B_4  | Write | Expansion port 4 – write 16 bits to exp bus with decode 4 active |

| 3402A  | Exp_Port_B_5  | Write | Expansion port 5 – write 16 bits to exp bus with decode 5 active |

| 3402C  | Exp_Port_B_6  | Write | Expansion port 6 – write 16 bits to exp bus with decode 6 active |

| 3402E  | Exp_Port_B_7  | Write | Expansion port 7 – write 16 bits to exp bus with decode 7 active |

| 34030  | Ion_Port_1    | R/W   | Read/Write contents of ion-counter 1 (diagnostic only)           |

| 34032  | Ion_port_2    | R/W   | Read/Write contents of ion-counter 2 (diagnostic only)           |

| 34034  | Chan_port     | R/W   | Low 10 bits hold channel count, incremented by chan_inc          |

| 34036- | Not used      |       |                                                                  |

| 3403E  |               |       |                                                                  |

#### 2.5.1 FIFO\_Port\_1 – FIFO low 16 bits permanent read

This is a read-only port that returns the low 16 bits of the next word from the FIFO. The 26 bit count/channel number is then removed from the FIFO. In order not to loose bits 25:16 of the FIFO entry, these should be read from FIFO\_Port2 before reading bits 15:0 from FIFO\_Port\_1

| MS  |     |                                                |  |  | F | IFO_P | ort_1( | 34000 | H) Rea | d |  |  |    |  | LS |

|-----|-----|------------------------------------------------|--|--|---|-------|--------|-------|--------|---|--|--|----|--|----|

| 15  | 14  | 14 13 12 11 10 9 8 7 6 5 4 3 2 1               |  |  |   |       |        |       |        |   |  |  |    |  | 0  |

| D15 | D14 | D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 |  |  |   |       |        |       |        |   |  |  | D0 |  |    |

This word contains the counts for an element of an ion-trap spectrum. Bit 15, once set remains at 1 as an indication that the count has overflowed the lower 15 bits.

### **Ptolemy Hardware/Software Interface Document**

Issue: 5

**Document Number**: RO-LPT-OU-TN-3401

Date: 3rd April 2001

#### 2.5.2 FIFO\_Port\_2 – FIFO high bits and flags interrogative read

This is a read-only port that returns the following data:

| MS |    |                                  |       |  | F | 'IFO_P | ort_2 ( | 34002 | H) Rea | d   |     |     |     |     | LS  |

|----|----|----------------------------------|-------|--|---|--------|---------|-------|--------|-----|-----|-----|-----|-----|-----|

| 15 | 14 | 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |       |  |   |        |         |       |        |     |     |     |     |     |     |

| FV |    | FIFO                             | error |  | 0 | D25    | D24     | D23   | D22    | D21 | D20 | D19 | D18 | D17 | D16 |

Where:

| FV         | FIFO_validB - should    | d be 0 for valid data                                             |  |  |  |  |  |  |  |  |

|------------|-------------------------|-------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| FIFO error | FIFO error bits         | x1xx – FIFO has fewer words that indicated by count               |  |  |  |  |  |  |  |  |

|            | should be all 0         | iould be all 0 1xxx – FIFO has more words than indicated by count |  |  |  |  |  |  |  |  |

| Bit 10     | Always 0                |                                                                   |  |  |  |  |  |  |  |  |

| D25-D16    | This field contains the | e top 10 bits of the next 26 bit value in the FIFO. This          |  |  |  |  |  |  |  |  |

|            | corresponds to the cha  | corresponds to the channel number for the count in FIFO_Port_1    |  |  |  |  |  |  |  |  |

Before reading FIFO\_Port\_1, this port should be read to get bits 25-16 (top 10 bits) of the 26 bit count+channel entry. Bits 10 to 15 of this word (top 6 bits) should be 0, any other combination constitutes an error.

#### 2.5.3 FIFO\_Port\_3 FIFO full/empty status

This is a read-only port that reports the state of the 26-bit-wide FIFO:

| MS |    |    |    |    | F                    | IFO_P | ort_3 (      | 34004 | H) Rea | d |  |  |  |  | LS |  |

|----|----|----|----|----|----------------------|-------|--------------|-------|--------|---|--|--|--|--|----|--|

| 15 | 14 | 13 | 12 | 11 | 10 9 8 7 6 5 4 3 2 1 |       |              |       |        |   |  |  |  |  |    |  |

| FE | FF | 0  | 0  | 0  | 0                    |       | FIFO howFull |       |        |   |  |  |  |  |    |  |

| FF           | - FIFO full flag. =1 if FIFO is full, =0 if FIFO is not full                  |

|--------------|-------------------------------------------------------------------------------|

| FE           | - FIFO empty flag. =1 if FIFO is empty, =0 if FIFO is full                    |

| FIFO_howFull | - FIFO contents count – count of number of entries remaining in FIFO (0-1023) |

#### 2.5.4 FIFO\_Port\_4 FIFO flip bits 15:0

This read-write register allows the software to set and read the lower 16 bits of the 31-bit FIFO flip register. This may be used to corrupt deliberately the contents of the FIFO for test purposes.

| MS |                     |                                  |  |  | FIFC | )_Port | _4 (340 | )06H) | Read/W | Vrite |  |  |  |   | LS |

|----|---------------------|----------------------------------|--|--|------|--------|---------|-------|--------|-------|--|--|--|---|----|

| 15 | 14                  | 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |  |  |      |        |         |       |        |       |  |  |  | 0 |    |

|    | FIFO flip bits 15:0 |                                  |  |  |      |        |         |       |        |       |  |  |  |   |    |

#### 2.5.5 FIFO\_Port\_5 FIFO flip bits 30:16

This read-write register allows the software to set and read the upper 15 bits of the 31 bit FIFO flip register.

| MS |    |    |    |    | FIFC | D_Port | _5 (340 | (H800    | Read/W | Vrite |   |   |   |   | LS |

|----|----|----|----|----|------|--------|---------|----------|--------|-------|---|---|---|---|----|

| 15 | 14 | 13 | 12 | 11 | 10   | 9      | 8       | 7        | 6      | 5     | 4 | 3 | 2 | 1 | 0  |

| 0  |    |    |    |    |      |        | FIFO f  | lip bits | 30:16  |       |   |   |   |   |    |

Bit 15 is not used and always reads 0. Bits 14:0 control FIFO flip bits 30:16.

### **Ptolemy Hardware/Software Interface Document**

Issue: 5

Document Number: RO-LPT-OU-TN-3401

Date: 3rd April 2001

#### 2.5.6 FIFO\_Port\_6 FIFO vector

This read-only register allows the software to read the FIFO vector, a 5 bit value

| MS |    |    |    |    | FIF | D_Port | _6 (34 | 00AH) | Read | only |   |    |        |     | LS |

|----|----|----|----|----|-----|--------|--------|-------|------|------|---|----|--------|-----|----|

| 15 | 14 | 13 | 12 | 11 | 10  | 9      | 8      | 7     | 6    | 5    | 4 | 3  | 2      | 1   | 0  |

| 0  | 0  | 0  | 0  | 0  | 0   | 0      | 0      | 0     | 0    | 0    |   | FI | FO vec | tor |    |

#### 2.5.7 FIFO\_Port\_7 Test data/Test count/Test result

This is a read/write register. The software writes test data to bits 15-10 and the test count to bits 9-0:

| MS |    |      |      |    | F  | FO_P | ort_7 (. | 3400C | H) Wri | te   |       |   |   |   | LS |

|----|----|------|------|----|----|------|----------|-------|--------|------|-------|---|---|---|----|

| 15 | 14 | 13   | 12   | 11 | 10 | 9    | 8        | 7     | 6      | 5    | 4     | 3 | 2 | 1 | 0  |

|    |    | Test | data |    |    |      |          |       |        | Test | count |   |   |   |    |

The test count and test result can be read from the same address:

| MS |    |    |    |    | F  | IFO_P | ort_7 ( | 3400C | H) Rea | ıd   |       |   |   |   | LS |

|----|----|----|----|----|----|-------|---------|-------|--------|------|-------|---|---|---|----|

| 15 | 14 | 13 | 12 | 11 | 10 | 9     | 8       | 7     | 6      | 5    | 4     | 3 | 2 | 1 | 0  |

| TC | TS | TF | 0  | 0  | 0  |       |         |       |        | Test | count |   |   |   |    |

TC - Test complete – set when test is complete

TS - Test success – set if test was successful

TF - Test fail – set if test failed

#### 2.5.8 FIFO\_Port\_8 read code

This read-only register allows the software to read the 31 bit code. Bits 15:0 are read if the test\_mux field is 0. Bits 30:16 are read if the test\_mux field is 1. The test\_mux bit is in the Softt\_Ctrl\_Port register.

| MS |    |    |    | Fl | FO_Po | ort_8 (. | 3400EI  | H) Rea  | d (test_ | _mux= | 0) |   |   |   | LS |

|----|----|----|----|----|-------|----------|---------|---------|----------|-------|----|---|---|---|----|

| 15 | 14 | 13 | 12 | 11 | 10    | 9        | 8       | 7       | 6        | 5     | 4  | 3 | 2 | 1 | 0  |

|    |    |    |    |    |       |          | code bi | ts 15:0 | )        |       |    |   |   |   |    |

| MS |    |    |    | F  | FO_Po | ort_8 (1 | 3400EI | H) Rea   | d (test_ | _mux= | 1) |   |   |   | LS |

|----|----|----|----|----|-------|----------|--------|----------|----------|-------|----|---|---|---|----|

| 15 | 14 | 13 | 12 | 11 | 10    | 9        | 8      | 7        | 6        | 5     | 4  | 3 | 2 | 1 | 0  |

| 0  |    |    |    |    |       |          | Code   | e bits 3 | 0:16     |       |    |   |   |   |    |

#### 2.5.9 I2C\_Port\_1 – read/write I2C data

This Port allows data to be written to the I2C port for transmission, received data to be read from the I2C port and the status of the I2C port to be read

Writing a byte to I2C\_Port\_1 causes it to be transmitted via the I2C interface:

| MS |    |    |         |    | Ι  | 2C_Po | ort_1 (3 | 4010H | l) Write | e |        |          |   |   | LS |

|----|----|----|---------|----|----|-------|----------|-------|----------|---|--------|----------|---|---|----|

| 15 | 14 | 13 | 12      | 11 | 10 | 9     | 8        | 7     | 6        | 5 | 4      | 3        | 2 | 1 | 0  |

|    |    | N  | lot use | d  |    |       | lbyt     |       |          | 1 | Transn | nit data | ι |   |    |

### **Ptolemy Hardware/Software Interface Document**

Issue: 5

**Document Number:** RO-LPT-OU-TN-3401

Date: 3rd April 2001

The bit lbyt (bit 8) is set by the software to indicate the last byte of a message.

Reading a byte from I2C\_Port\_1 removes a data byte from the received data field (if any) and returns the interface status:

| MS |    |         |    |    | ]    | 2C_Po | ort_1 (3 | 34010H | I) Read | 1  |        |        |     |   | LS |

|----|----|---------|----|----|------|-------|----------|--------|---------|----|--------|--------|-----|---|----|

| 15 | 14 | 13      | 12 | 11 | 10   | 9     | 8        | 7      | 6       | 5  | 4      | 3      | 2   | 1 | 0  |

|    | N  | lot use | d  |    | abrt | rcv   | tx       |        |         | Re | ceived | data b | yte |   |    |

|    |    |         |    |    |      | ept   | free     |        |         |    |        |        |     |   |    |

| Bits  | Desg          | Description                                                              |

|-------|---------------|--------------------------------------------------------------------------|

| 15:11 | Not used      | Unused bits                                                              |

| 10    | abrt          | If set, operation aborted                                                |

| 9     | rcv ept       | If set, the receive data register is empty (no new receive data)         |

| 8     | tx free       | If set, the transmit register is free (next byte of data may be written) |

| 7:0   | Received data | Last received byte                                                       |

This read of the received data register is destructive, after the read, the next byte of received data may replace the contents of the receive register.

#### 2.5.10 I2C\_Port\_2 – non-destructive read of I2C received data

This is a non-destructive read, the data remains in the receive register, reception of further words is not enabled. This address should be used to check on the interface status.

| MS |    |         |    |    | l    | 2C_Po | ort_2 (3 | 34012F | I) Read | 1  |        |        |     |   | LS |

|----|----|---------|----|----|------|-------|----------|--------|---------|----|--------|--------|-----|---|----|

| 15 | 14 | 13      | 12 | 11 | 10   | 9     | 8        | 7      | 6       | 5  | 4      | 3      | 2   | 1 | 0  |

|    | N  | lot use | d  |    | abrt | rcv   | tx       |        |         | Re | ceived | data b | yte |   |    |

|    |    |         |    |    |      | ept   | free     |        |         |    |        |        |     |   |    |

#### 2.5.11 Soft\_Ctrl\_Port

This read/write port allows the software to reset and configure various RICA functions.

| MS |    |    |    |    | Soft_ | Ctrl_P | ort (34 | 014H) | Read/ | Write |     |     |     |     | LS  |

|----|----|----|----|----|-------|--------|---------|-------|-------|-------|-----|-----|-----|-----|-----|

| 15 | 14 | 13 | 12 | 11 | 10    | 9      | 8       | 7     | 6     | 5     | 4   | 3   | 2   | 1   | 0   |

| 0  | 0  | 0  | 0  | 0  | 0     | 0      | 0       | 0     | Wd    | Tst   | Tst | Tst | Ct  | Fif | I2c |

|    |    |    |    |    |       |        |         |       | rs    | Mx    | m2  | m1  | rst | rst | rst |

| Bit  | Desg.   | Function        |                                                                                    |  |  |  |  |  |  |

|------|---------|-----------------|------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 15:7 | 0       | Not used – re   | ead as 0                                                                           |  |  |  |  |  |  |

| 6    | Wd rs   | Set to reset of | n-chip watchdog timer – not used on Ptolemy                                        |  |  |  |  |  |  |

| 5    | Tst mx  | Test_mux        | =0: FIFO_Port_8 reads bits 15:0 of 31 bit FIFO code                                |  |  |  |  |  |  |

|      |         |                 | =1: FIFO_Port_8 reads bits 30:16 of 31 bit FIFO code When set, selects test mode 2 |  |  |  |  |  |  |

| 4    | Tst m2  | When set, se    | When set, selects test mode 2                                                      |  |  |  |  |  |  |

| 3    | Tst m1  | When set, se    | lects test mode 1                                                                  |  |  |  |  |  |  |

| 2    | Ct rst  | Writing a zer   | to to this bit asserts the count reset, writing a 1 releases it                    |  |  |  |  |  |  |

| 1    | Fif rst | Writing a zer   | ro to this bit asserts the FIFO reset, writing a 1 releases it                     |  |  |  |  |  |  |

| 0    | I2c rst | Writing a zer   | ro to this bit asserts the I2C reset, writing a 1 releases it                      |  |  |  |  |  |  |

2.5.12 DACC\_Port – DAC counter port

### **Ptolemy Hardware/Software Interface Document**

Issue: 5

**Document Number**: RO-LPT-OU-TN-3401

Date: 3rd April 2001

This read/write port allows software acces to the DAC counter port. This value is output as a 12 bit parallel signal for conversion by a DAC to control the RF signal amplitude. The DAC value can be incremented or decremented by pulses from the WGA without software intervention

| MS |    |                                                                                      |   |  | DA                | CC_Po | ort (340 | )16H) | Read/w | rite |  |  |  |  | LS |

|----|----|--------------------------------------------------------------------------------------|---|--|-------------------|-------|----------|-------|--------|------|--|--|--|--|----|

| 15 | 14 | 14     13     12     11     10     9     8     7     6     5     4     3     2     1 |   |  |                   |       |          |       |        |      |  |  |  |  |    |

| 0  | 0  | 0                                                                                    | 0 |  | Current DAC value |       |          |       |        |      |  |  |  |  |    |

#### 2.5.13 RFClk\_Port\_1 – RF clock generator I/F port 1

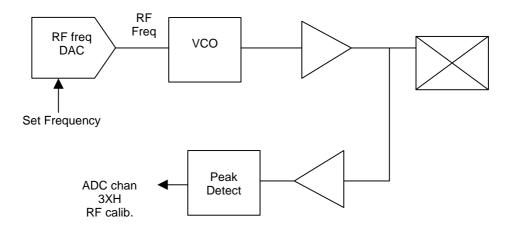

This read/write port allows the software to set and read back the divider that controls RF clock 1. The RF frequency shall be 4194304 Hz divided by the value in RFClk\_Port\_1 This register is not used to control the Ptolemy RF clock – a VCO circuit is used that gives better resolution.

| MS |                                                                                      |   |   |   | RFC | lk_Por | t_1 (34 | 4018H) | Read/ | write |  |  |  |  | LS |

|----|--------------------------------------------------------------------------------------|---|---|---|-----|--------|---------|--------|-------|-------|--|--|--|--|----|

| 15 | 14     13     12     11     10     9     8     7     6     5     4     3     2     1 |   |   |   |     |        |         |        |       |       |  |  |  |  | 0  |

| 0  | 0                                                                                    | 0 | 0 | 0 | 0   | 0      |         |        |       |       |  |  |  |  |    |

#### 2.5.14 RFClk\_Port\_2 - RF clock generator I/F port 2 - tickle clock

This read/write port allows the software to set and read back the divider that controls RF clock 2. The RF tickle frequency shall be 4194304 Hz divided by the value in RFClk\_Port\_2 This is not used on Ptolemy as the tickle signal has been removed from the design:

| MS |                                                                                      |   |   |   | RFC | lk_Por | t_1 (34            | 018H) | Read/ | write |  |  |  |  | LS |  |  |

|----|--------------------------------------------------------------------------------------|---|---|---|-----|--------|--------------------|-------|-------|-------|--|--|--|--|----|--|--|

| 15 | 14     13     12     11     10     9     8     7     6     5     4     3     2     1 |   |   |   |     |        |                    |       |       |       |  |  |  |  | 0  |  |  |

| 0  | 0                                                                                    | 0 | 0 | 0 | 0   | 0      | RF clock 2 divider |       |       |       |  |  |  |  |    |  |  |

#### 2.5.15 Assignment of WGA outputs

The WGA is programmed via the RICA  $I^2C$  interface. Details of the WGA operation are described in RD3. Specific to Ptolemy, however, are the following bit assignments for WGA outputs:

| WGA bit    | Function                            |

|------------|-------------------------------------|

| 0 (LS bit) | Incremnet Ring RF (DAC_up)          |

| 1          | Decrement Ring RF (DAC_Down)        |

| 2          | Increment Channel Number (Chan_inc) |

| 3          | Extractor/Nanotip                   |

| 4          | Electron Repeller/Gate2             |

| 5          | -                                   |

| 6          | -                                   |

| 7          | Ion_trap_inp2                       |

#### 2.6 DC DAC outputs

The DC DAC is used to set each of the DC voltage levels required to operate the various items in the science system. The RF amplitude voltage is set via a separate DAC, controlled by the WGA via the RICA.

#### 2.6.1 The DAC output/channel select register

To set the output level for one of the DACs, the software shall write a 16 bit word to the port at address 3C080H containing the 8 bit value to output and the 4 bit address of the channel to be set:

### **Ptolemy Hardware/Software Interface Document**

Issue: 5

Document Number: RO-LPT-OU-TN-3401

Date: 3rd April 2001

| MS |                                  |  |  |  | DC | DAC o | control | (3C08 | 0H): W | /rite |  |    |        |         | LS   |

|----|----------------------------------|--|--|--|----|-------|---------|-------|--------|-------|--|----|--------|---------|------|

| 15 | 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |  |  |  |    |       |         |       |        |       |  |    |        |         | 0    |

|    | DAC o/p value (0-255)            |  |  |  |    |       |         |       | not    | used  |  | DA | C chan | sel (0- | -15) |

After writing a value to the DC DAC control register, it is recommended to wait ~1ms (TBC) before writing a subsequent value (i.e for a different DAC channel) to allow time for the current channel to charge.

In order to maintain the output voltage of a channel constant to within  $\pm 1$  lsb, it is recommended that each channel be refreshed (re-written) no less frequently than every 64ms (TBC).

#### 2.6.2 DAC channel enables

This 16 bit register shall be implemented with an enable/disable bit for each analogue channel

| MS  |     |                                                                                                                                          |     | Ι   | DC DA | C enal | ole regi | ister (3 | 8090H | ) Write | e   |     |     |     | LS  |

|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|--------|----------|----------|-------|---------|-----|-----|-----|-----|-----|

| 15  | 14  | 14         13         12         11         10         9         8         7         6         5         4         3         2         1 |     |     |       |        |          |          |       |         |     |     |     |     | 0   |

| spr | c14 | c13                                                                                                                                      | c12 | c11 | c10   | c09    | c08      | c07      | c06   | c05     | c04 | c03 | c02 | c01 | c00 |

cnn enable/disable bit for channel nn bit set for enable, reset for disable

spr spare channel enable/disable bit

The DC DAC channel enable registers shall be initialised to 0 at power-on (all channels disabled) but the software should also write zeros to these registers as part of safe-mode initialisation as a precaution against possible failure of initialisation by the FPGA.

#### 2.6.3 DC DAC channel assignments

The channels are assigned to analogue outputs as follows:

| Chan | Description                                       | 1 DAC lsb | remarks        |

|------|---------------------------------------------------|-----------|----------------|

| 00   | Ion Trap DC control 1 (extractor voltage)         |           |                |

| 01   | Ion Trap DC control 2 (electron gate 1 voltage)   |           |                |

| 02   | Ion Trap DC control 3 (electron repeller voltage) |           |                |

| 03   | Ion Trap DC control 4 (electron gate 2 voltage)   |           |                |

| 04   | Nanotip current                                   |           |                |

| 05   | HT (2.5kV) voltage                                |           |                |

| 06   | Docking station DC motor drive upper position     |           | see 2.9.3      |

| 07   | Docking station DC motor drive lower position     |           | see 2.9.3      |

| 08   | hLV1 – Lindau valve LV1 heater                    |           |                |

| 09   | hLV2 – Lindau valve LV2 heater                    |           |                |

| 10   | deleted                                           |           | was LV3 heater |

| 11   | deleted                                           |           | was LV4 heater |

| 12   | hLV5 – Lindau valve LV5 heater                    |           |                |

| 13   | hLV6 – Lindau valve LV6 heater (formerly RV1)     |           |                |

| 14   | hLV7 – Lindau valve LV7 heater (formerly RV2)     |           |                |

| 15   | Spare                                             |           |                |

Channels 6 and 7 are used to set target (limiting) postitions when driving the docking station. The motor drive shall fall to 0 when the target position is reached or passed. This reduces the timing demands on the flight software when operating the docking station.

### **Ptolemy Hardware/Software Interface Document**

Issue: 5

Document Number: RO-LPT-OU-TN-3401

Date: 3rd April 2001

#### 2.7 PWM output channels

These digital (on/off) channels switch power to reactors and heaters. A 16 bit register at address 380C0H contains 1 bit for each output. Setting a bit to 1 shall switch on the corresponding output and setting a bit to 0 shall switch off the corresponding output. These Channels are intended to be used with software PWM – Each channel to be activated shall be assigned a time window in a repeating 0.25s (TBC) period. The heating effect shall be modulated by varying the period for which the channel is actually pulsed on within this window.

A second 16 bit register at location 380D0H shall contain an enable/disable bit for each output. Setting a bit in this register to 1 shall enable the corresponding output, setting it to 0 shall disable the corresponding output.

#### 2.7.1 PWM output control register

| MS  |     |                                  |     |     | PWN | M O/P | registe | r (3800 | C0H) V | Vrite |     |     |     |     | LS  |

|-----|-----|----------------------------------|-----|-----|-----|-------|---------|---------|--------|-------|-----|-----|-----|-----|-----|

| 15  | 14  | 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |     |     |     |       |         |         |        |       |     |     |     |     |     |

| c15 | c14 | c13                              | c12 | c11 | c10 | c09   | c08     | c07     | c06    | c05   | c04 | c03 | c02 | c01 | c00 |

cnn on/off bit for channel nn bit set for on, reset for off

spr spare channel on/off bit

#### 2.7.2 PWM output enable register

| MS  |     |                                  |     | Р   | WM O | /P ena | ble reg | ister (3 | 80D0F | H) Wri | te  |     |     |     | LS  |

|-----|-----|----------------------------------|-----|-----|------|--------|---------|----------|-------|--------|-----|-----|-----|-----|-----|

| 15  | 14  | 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |     |     |      |        |         |          |       |        |     |     |     |     | 0   |

| c15 | c14 | c13                              | c12 | c11 | c10  | c09    | c08     | c07      | c06   | c05    | c04 | c03 | c02 | c01 | c00 |

cnn enable/disable bit for channel nn bit set for enable, reset for disable spr spare channel enable/disable bit

#### 2.7.3 PWM output channel assignments

| Chan | Description                                 |

|------|---------------------------------------------|

| 00   | Reactor R1 heater                           |

| 01   | Reactor R2 heater                           |

| 02   | Reactor R4 heater (reactor 3 deleted)       |

| 03   | Reactor R5 heater                           |

| 04   | Reactor R6 heater                           |

| 05   | Reactor R7 heater                           |

| 06   | Reactor R8 heater                           |

| 07   | Reactor R9/R14 heater                       |

| 08   | Reactor R13 heater (reactors 10-12 deleted) |

| 09   | Reactor R15 heater                          |

| 10   | GC heater                                   |

| 11   | ENC1 Heater                                 |

| 12   | ENC2 Heater                                 |

| 13   | Ion Trap heater                             |

| 14   | Transfer pipe heater                        |

| 15   | Oven heater                                 |

### **Ptolemy Hardware/Software Interface Document**

Issue: 5

Document Number: RO-LPT-OU-TN-3401

Date: 3rd April 2001

#### 2.8 Digital (On/Off) channels

These channels appear to the software as simple on/off controls. Any pulse timing required shall be performed in hardware.

#### 2.8.1 Digital (On/Off) output control register

| MS  |     |                                  |     | Dig | gital (C | n/Off) | O/P re | gister | (380A | 0H) W | rite |     |     |     | LS  |

|-----|-----|----------------------------------|-----|-----|----------|--------|--------|--------|-------|-------|------|-----|-----|-----|-----|

| 15  | 14  | 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |     |     |          |        |        |        |       |       |      |     |     |     |     |

| c15 | c14 | c13                              | c12 | c11 | c10      | c09    | c08    | c07    | c06   | c05   | c04  | c03 | c02 | c01 | c00 |

cnn on/off bit for channel nn bit set for on, reset for off

#### 2.8.2 Digital (On/Off) output enable register

| MS  |                                  |     |     | Digital | (On/C | Off) O/ | P enabl | le regis | ster (38 | OB0H) | ) Write |     |     |     | LS  |

|-----|----------------------------------|-----|-----|---------|-------|---------|---------|----------|----------|-------|---------|-----|-----|-----|-----|

| 15  | 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |     |     |         |       |         |         |          |          |       |         |     |     |     | 0   |

| c15 | c14                              | c13 | c12 | c11     | c10   | c09     | c08     | c07      | c06      | c05   | c04     | c03 | c02 | c01 | c00 |

cnn enable/disable bit for channel nn bit set for enable, reset for disable

#### 2.8.3 On/Off channel assignments:

| Chan | Description |                        |

|------|-------------|------------------------|

| 00   | CV1         | Clipard Valve          |

| 01   | CV2         | Clipard Valve          |

| 02   | CV3         | Clipard Valve          |

| 03   | CV4         | Clipard Valve          |

| 04   | CV7         | Clipard Valve          |

| 05   | CV8         | Clipard Valve          |

| 06   | CV9         | Clipard Valve          |

| 07   | CV10        | Clipard Valve          |

| 08   | CV11        | Clipard Valve (3-way)  |

| 09   | CV13        | Clipard Valve          |

| 10   | CV14        | Clipard Valve          |

| 11   | CV15        | Clipard Valve          |

| 12   | CV16        | Clipard Valve (3-way)  |

| 13   | CVA         | Injector control valve |

| 14   | CVB         | Injector control valve |

| 15   | CVC         | Injector control valve |

#### 2.9 Critical function channels

These channels control critical functions which could endanger instrument survivability if activated at the wrong time. Each of these functions has a corresponding enabable bit in the Critical functions enable register.

#### 2.9.1 Critical functions register

| MS Critical functions register (380E0H) Write |          |                                  |  |  |  |  |  |    |    | LS |   |   |    |    |

|-----------------------------------------------|----------|----------------------------------|--|--|--|--|--|----|----|----|---|---|----|----|

| 15                                            | 14       | 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |  |  |  |  |  |    |    |    |   |   | 0  |    |

|                                               | not used |                                  |  |  |  |  |  | MU | MD | HT | - | - | R2 | R1 |

### **Ptolemy Hardware/Software Interface Document**

Issue: 5

Document Number: RO-LPT-OU-TN-3401

Date: 3rd April 2001

| HT    | Set to switch on the High Tension, nanotip and extractor supplies to the Ion-trap. These should only be activated when the instrument is in a vacuum. |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| R1-R2 | Rupture valve outputs. To activate a rupture valve heater, the corresponding bit must be                                                              |

|       | cycled between 0 and 1 with a frequency of not less than 8KHz (TBC).                                                                                  |

| MD    | Motor Down drive enable – allows docking station motor to drive down (dock)                                                                           |

| MU    | Motor Up drive enable – allows docking station motor to drive up (undock)                                                                             |

#### 2.9.2 Critical functions enable register

| MS Critical functions enable register (380F0H) Write |    |                                  |  |  |  |    |    |    |   | LS |    |    |   |

|------------------------------------------------------|----|----------------------------------|--|--|--|----|----|----|---|----|----|----|---|

| 15                                                   | 14 | 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |  |  |  |    |    |    |   |    |    |    | 0 |

| not used                                             |    |                                  |  |  |  | MU | MD | HT | - | -  | R2 | R1 |   |

HT, R1,R2, MU and MD represent enables for the 5 critical function channels. These bits must be set for the critical function to operate.

#### 2.9.3 Operation of the docking station.

To enable a docking station operation, the appropriate bit (MU or MD) must be set in the critical functions enable register (2.9.2, above).

To operate the docking station, the upper and lower docking station positions (DC DAC channels 6 &7 repectively – see 2.6.3) should first be set to the desired limits of travel. MD may then be set to start the docking station driving down or MU to start it driving up. When the docking station reaches the corresponding limit of travel (i.e is outside the range set by DC DAC channels 6 & 7), the motor shall be stopped by hardware intervention. When the software observes that the station has reached the desired position, or after an appropriate timeout, the software should reset the motor drive bit (MD for downward movement, MU for upward movement).

This scheme is intended to free the software from the need to check the docking station position with a high time resolution.

After a docking station operation, the motor drive enable bits (MU&MD) should be reset in the Critical functions enable register.